Difference between revisions of "Application Note 3: Designing A Slot-Coupled Patch Antenna Array With A Corporate Feed Network Using EM.Picasso"

Kazem Sabet (Talk | contribs) (→Constructing a Four-Element Patch Sub-Array) |

Kazem Sabet (Talk | contribs) (→Constructing a Four-Element Patch Sub-Array) |

||

| Line 103: | Line 103: | ||

== Constructing a Four-Element Patch Sub-Array == | == Constructing a Four-Element Patch Sub-Array == | ||

| − | A binary H-tree structure is used to construct a 1:4 Wilkinson power divider network as shown in the figures below. In this case, the network involves three ring-type Wilkinson power dividers. | + | A binary H-tree structure is used to construct a 1:4 Wilkinson power divider network as shown in the figures below. In this case, the network involves three ring-type Wilkinson power dividers. |

| + | |||

<table> | <table> | ||

<tr> | <tr> | ||

| Line 167: | Line 168: | ||

<td> | <td> | ||

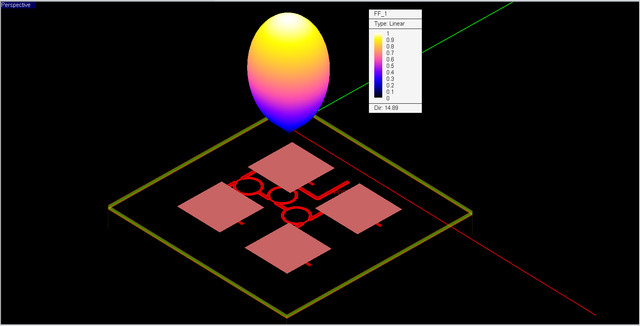

[[Image:ART PATCH Fig5.png|thumb|left|640px|3D radiation pattern of the 4-element patch sub-array computed at 2.4GHz.]] | [[Image:ART PATCH Fig5.png|thumb|left|640px|3D radiation pattern of the 4-element patch sub-array computed at 2.4GHz.]] | ||

| + | </td> | ||

| + | </tr> | ||

| + | </table> | ||

| + | |||

| + | == Constructing a 16-Element Patch Array == | ||

| + | |||

| + | <table> | ||

| + | <tr> | ||

| + | <td> | ||

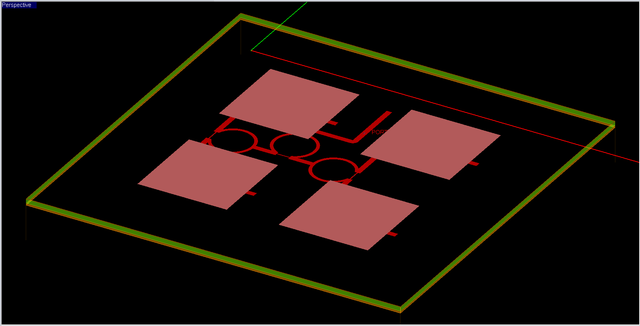

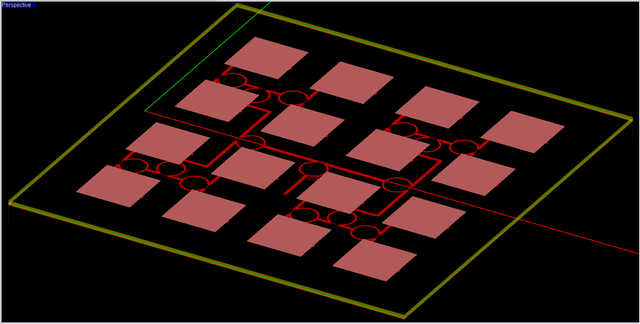

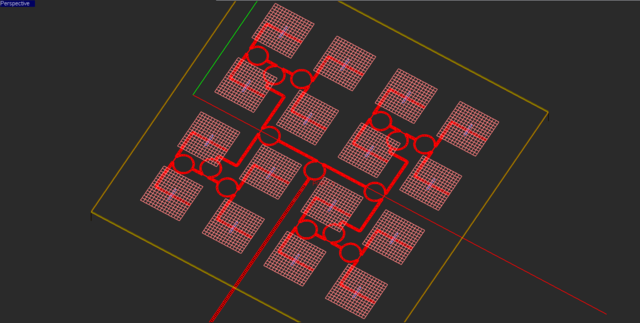

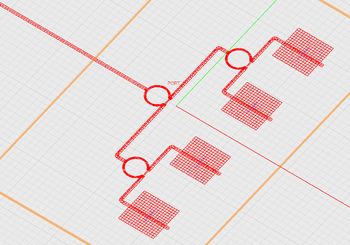

| + | [[Image:ART PATCH Fig10.png|thumb|left|640px|The geometry of the 16-element slot-coupled patch array with a corporate feed network.]] | ||

| + | </td> | ||

| + | </tr> | ||

| + | </table> | ||

| + | |||

| + | <table> | ||

| + | <tr> | ||

| + | <td> | ||

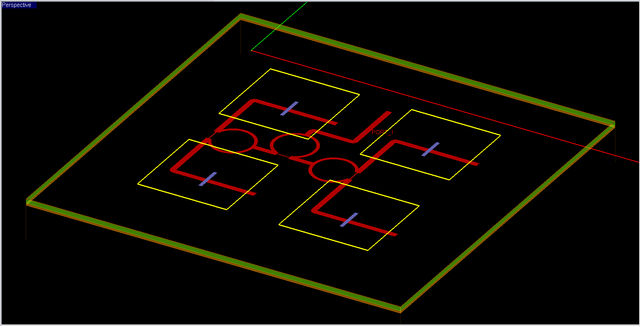

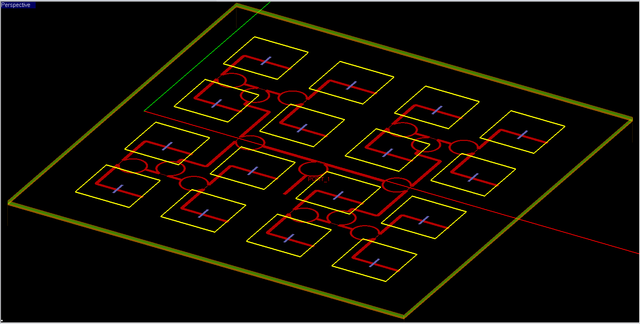

| + | [[Image:ART PATCH Fig11.png|thumb|left|640px|The geometry of the 16-element slot-coupled patch array with the patches in the freeze state.]] | ||

| + | </td> | ||

| + | </tr> | ||

| + | </table> | ||

| + | |||

| + | <table> | ||

| + | <tr> | ||

| + | <td> | ||

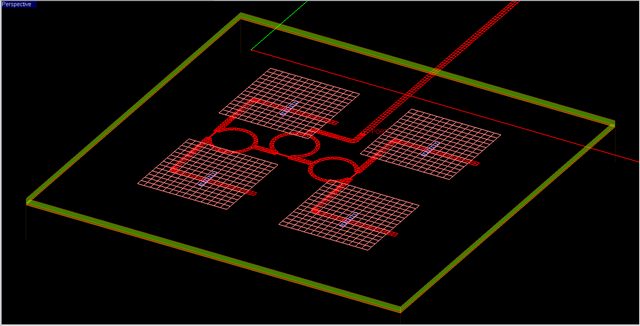

| + | [[Image:ART PATCH Fig12.png|thumb|left|640px|The hybrid planar mesh of the 16-element slot-coupled patch array with a corporate feed network.]] | ||

</td> | </td> | ||

</tr> | </tr> | ||

Revision as of 02:48, 17 October 2016

Contents

- 1 Introduction

- 2 Designing the Patch Radiating Element

- 3 Designing the Wilkinson Power Divider

- 4 Constructing a Four-Element Patch Sub-Array

- 5 Constructing a 16-Element Patch Array

- 6 Building the Array Structure

- 7 Examining the Mesh of the Planar Array

- 8 Running a Planar MoM Analysis of the Antenna Array

- 9 Comparison with Array Factor Method

Introduction

EM.Picasso can be used to analyze large and fairly complex multilayer planar structures. In this application note, we will show how to use EM.Picasso to design a 4 × 4 slot-coupled patch antenna array with a microstrip corporate feed network. The design process involves three steps: design of the slot-couple patch element, design of the power divider, and finally, construction of the 16-element array. The first two steps are the subject of two of EM.Picasso's tutorial lessons.

Designing the Patch Radiating Element

The operating frequency of the patch array is f = 2.4GHz. At this frequency, the free-space wavelength is λ0 = 125mm. The patch radiators will be spaced at half free-space wavelength: Sx = Sy = λ0/2 = 62.5mm. The design of the slot-coupled patch antenna is described in detail in EM.Picasso Tutorial Lesson 7: Designing A Slot-Coupled Patch Antenna. The substrate consists of two finite-thickness dielectric layers with εr = 3.38, σ = 0, separated by a perfect electric conductor (PEC) ground plane of infinite lateral extents. The table below summarizes the substrate stackup's layer hierarchy:

| Substrate Object Label | Substrate Object Type | Function | Material | Thickness |

|---|---|---|---|---|

| THS | Half-Space Medium | Top Substrate Termination | Vacuum | Infinite |

| PEC_1 | PEC Trace | Patch Plane | PEC | 0 |

| Layer_1 | Substrate Layer | Patch Substrate | ROGER RO4003C | 2mm |

| PMC_1 | Slot Trace | Slot Plane | PMC | 0 |

| Layer_2 | Substrate Layer | Feed Substrate | ROGER RO4003C | 0.787mm |

| PEC_2 | PEC Trace | Microstrip Feed Plane | PEC | 0 |

| BHS | Half-Space Medium | Bottom Substrate Termination | Vacuum | Infinite |

The design variables in this problem include the side dimensions of the square patch radiator, length and width of the coupling slot and the length of the open microstrip stub extended beyond the coupling slot. The width of the mircostrip feed line is chosen to be wf = 2.4mm to yield a characteristic impedance of Z0 = 50Ω.

| Design Variable Name | Optimal value |

|---|---|

| patch_len | 39.5mm |

| slot_len | 12mm |

| slot_wid | 1.5mm |

| stub_len | 21mm |

Designing the Wilkinson Power Divider

The input signal power must be divided equally among 16 patch radiating elements. In other words, a 1:16 power distribution network is needed for this project. The design of a Wilkinson power divider is described in detail in EM.Picasso Tutorial Lesson 9: Designing a Microstrip Wilkinson Power Divider. An Ω-shaped microstrip ring is used to create a three-port network. The input and output microstrip lines all have a width of 2.4mm with Z0 = 50Ω. The microstrip partial ring has a width of √2Z0 = 70.7Ω and serves as the two quarter-wave arms of the Wilkinson power divider. It is determined that if a lumped 100Ω resistor is connected between the two output arms of this divider, better return loss and isolation levels are achieved. The figure below shows the geometry of the optimized 1:2 Wilkinson power divider.

Constructing a Four-Element Patch Sub-Array

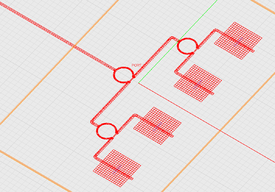

A binary H-tree structure is used to construct a 1:4 Wilkinson power divider network as shown in the figures below. In this case, the network involves three ring-type Wilkinson power dividers.

The multilayer structure is parameterized with the design variables listed in the table below. Of these variables, only the open stub length needs to be changed to 18.5mm, and rest of them retain their original value for the best input impedance match.

| Design Variable Name | Optimal value |

|---|---|

| patch_len | 39.5mm |

| slot_len | 12mm |

| slot_wid | 1.5mm |

| stub_len | 18.5mm |

| resistance | 100 Ohms |

The figure below shows the planar mesh of the sub-array. The patch and slot elements are discretized with a mesh density of 30 cells per effective wavelength, while the corporate feed network requires a higher mesh density of 50 cells per effective wavelength due to the narrow line hosting the lumped resistors.

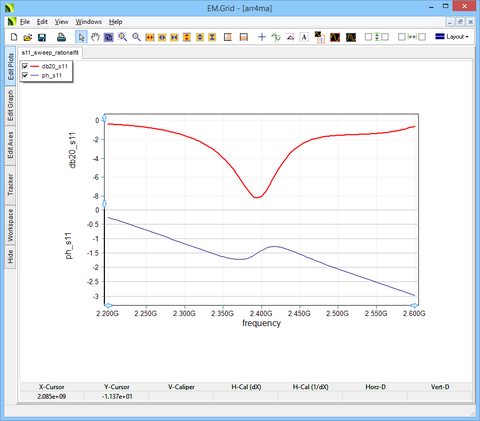

The 4-element slot-coupled patch sub-array is simulated using EM.Picasso's planar method of moments (MoM) solver. An adaptive frequency sweep is performed to compute the frequency response of the structure over the frequency range [2.2GHz - 2.6GHz]. The figures below show the variation of the sub-array's return loss with frequency and its 3D far-field radiation pattern computed at 2.4GHz.

Constructing a 16-Element Patch Array

Building the Array Structure

The corporate feed network on the microstrip trace plane (PEC_1) consists entirely of rectangle and circle strip objects. For the Wilkinson power dividers, circle strips with unequal outer and inner radii and incomplete start and end angles are used just as you saw in Tutorial Lesson 7. A 50Ω microstrip line on the lower thin substrate has a width of 2.4mm. Small circle strips of (outer) radius 2.4mm are used to provide a round bend junctions between two perpendicular microstrip line segments. Rather than a quarter-circle, a 3/4-circle shape is used to have some good overlap area over the conjoining line objects. This helps with a smoother and more consistent mesh in such junction areas.

Draw the following 9 circle strip objects, all on PEC_2 trace plane, with the given coordinates and dimensions:

|