Difference between revisions of "RF.Spice A/D Glossary"

| (3 intermediate revisions by the same user not shown) | |||

| Line 633: | Line 633: | ||

|- | |- | ||

|} | |} | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

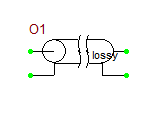

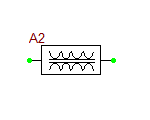

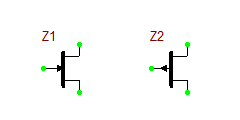

==Darlington Pair== | ==Darlington Pair== | ||

| Line 762: | Line 710: | ||

|} | |} | ||

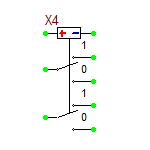

| − | == | + | ==D Flip-Flop== |

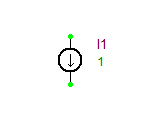

| − | [[File: | + | [[File:G52.png]] |

| − | + | The digital D-type flip-flop is a one-bit, edge-triggered storage element which stores data whenever the clock (CLK) input line transitions from 0 (low) to 1 (high). In addition, there are asynchronous set and reset signals, which are independent of the clock. When SET = RESET = 0, the data on the D line is transferred to the output Q on the rising edge of the clock. The combination SET = 1 and RESET = 0, causes Q = 1. The combination SET = 0 and RESET = 1 causes Q = 0. The combination SET = RESET = 1 is illegal and is resolved by setting both outputs Q and Q_bar to 1. | |

| − | + | Truth Table: | |

| − | {| class="wikitable" | + | <table> |

| + | <tr> | ||

| + | <td> | ||

| + | {| class="wikitable" | ||

|- | |- | ||

| − | ! | + | ! CLK !! D !! Q !! Notes |

|- | |- | ||

| − | | | + | |[[File:NonRising.png]] || X || Q<sub>prev</sub> || Hold State |

|- | |- | ||

| − | | | + | |[[File:Rising.png]] || 0 || 0 || Data Transfer |

|- | |- | ||

| − | | | + | |[[File:Rising.png]] || 1 || 1 || Data Transfer |

| − | + | ||

| − | + | ||

|- | |- | ||

|} | |} | ||

| + | </td> | ||

| + | </tr> | ||

| + | </table> | ||

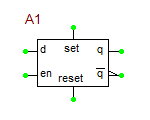

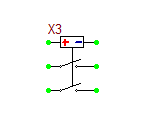

| − | == | + | ==D Latch== |

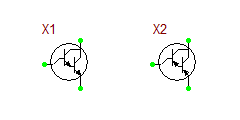

| − | [[File: | + | [[File:G54.png]] |

| − | The digital | + | The digital D-type latch is a one-bit, level-sensitive storage element which outputs the value on the data (D) line whenever the enable (EN) input line is 1 (high). The value on the data line is stored, i.e., held on the output (Q) line whenever the enable (EN) line is 0 (low). In addition, there are set and reset signals, which are independent of the enable line. When SET = RESET = 0, the data on the D line is transferred to the output Q whenever EN = 1. The combination SET = 1 and RESET = 0, causes Q = 1. The combination SET = 0 and RESET = 1 causes Q = 0. The combination SET = RESET = 1 is illegal and is resolved by setting both outputs Q and Q_bar to 1. |

| − | + | Truth Table: | |

| − | + | <table> | |

| − | + | <tr> | |

| − | + | <td> | |

| − | + | {| class="wikitable" | |

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | {| class="wikitable" | + | |

|- | |- | ||

| − | ! | + | ! EN !! D !! Q !! Notes |

|- | |- | ||

| − | | | + | |0 || X || Q<sub>prev</sub> || Hold State |

|- | |- | ||

| − | | | + | |1 || 0 || 0 || Reset |

|- | |- | ||

| − | | | + | |1 || 1 || 1 || Set |

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

|- | |- | ||

|} | |} | ||

| + | </td> | ||

| + | </tr> | ||

| + | </table> | ||

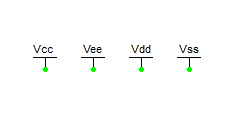

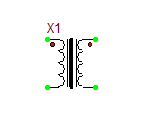

| − | == | + | == DC Bias Sources Vcc, Vee, Vdd, Vss == |

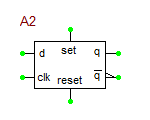

| − | [[File: | + | [[File:GL12.png]] |

| − | + | These are simple 1-pin DC voltage sources. Vcc and Vdd provide a positive voltage, while Vee and Vss provide a negative voltage | |

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

Parameters: | Parameters: | ||

| Line 844: | Line 774: | ||

!NAME!!PARAMETER!!UNIT!!DEFAULT!!NOTES | !NAME!!PARAMETER!!UNIT!!DEFAULT!!NOTES | ||

|- | |- | ||

| − | | | + | |vcc||bias voltage||V||+15||required |

|- | |- | ||

| − | | | + | |vee||bias voltage||V||-15||required |

|- | |- | ||

| − | | | + | |vdd||bias voltage||V||+15||required |

|- | |- | ||

| − | | | + | |vss||bias voltage||V||-15||required |

| − | |- | + | |

| − | + | ||

| − | + | ||

| − | + | ||

|- | |- | ||

|} | |} | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

==Digital-to-Analog Converter (DAC) Bridge== | ==Digital-to-Analog Converter (DAC) Bridge== | ||

| Line 1,244: | Line 1,136: | ||

|- | |- | ||

|fraction||smoothing fraction/absolute value switch||true | |fraction||smoothing fraction/absolute value switch||true | ||

| + | |- | ||

| + | |} | ||

| + | |||

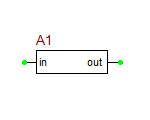

| + | ==Ideal Buffer Block== | ||

| + | |||

| + | [[File:GL40.png]] | ||

| + | |||

| + | This model is an ideal buffer block with a default unity gain. | ||

| + | |||

| + | Parameters: | ||

| + | |||

| + | {| class="wikitable" | ||

| + | |- | ||

| + | !NAME!!PARAMETER!!UNITS!!DEFAULT!!NOTES | ||

| + | |- | ||

| + | |r_in||input resistance||Ω||1G|| | ||

| + | |- | ||

| + | |r_out||output resistance||Ω||1u|| | ||

| + | |- | ||

| + | |gain||gain||-||1.0|| | ||

|- | |- | ||

|} | |} | ||

| Line 1,266: | Line 1,178: | ||

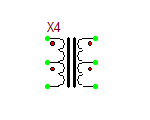

where v<sub>P</sub> is the primary voltage, v<sub>S1</sub> is measured between the top secondary pin S1 and the center tap pin, and v<sub>S2</sub> is measured between the center tap pin and the bottom secondary pin S2. The red dots show the polarity of the windings on each side. This model has one parameter: ratio = n = N<sub>P</sub>/N<sub>S1</sub> = N<sub>P</sub>/N<sub>S2</sub>, which represents the primary-to-secondary (half-winding) turns ratio. | where v<sub>P</sub> is the primary voltage, v<sub>S1</sub> is measured between the top secondary pin S1 and the center tap pin, and v<sub>S2</sub> is measured between the center tap pin and the bottom secondary pin S2. The red dots show the polarity of the windings on each side. This model has one parameter: ratio = n = N<sub>P</sub>/N<sub>S1</sub> = N<sub>P</sub>/N<sub>S2</sub>, which represents the primary-to-secondary (half-winding) turns ratio. | ||

| + | |||

| + | ==Ideal Comparator Block== | ||

| + | |||

| + | [[File:GL51.png]] | ||

| + | |||

| + | This block is an ideal two-signal voltage comparator with a default unity gain. It has a binary output that takes a value of 0V if v<sub>pos</sub> < v<sub>neg</sub> and takes a value of 1V if v<sub>pos</sub> > v<sub>neg</sub>. If v<sub>pos</sub> = v<sub>neg</sub>, the output voltage is 0.5V. | ||

| + | |||

| + | Parameters: | ||

| + | |||

| + | {| class="wikitable" | ||

| + | |- | ||

| + | !NAME!!PARAMETER!!UNITS!!DEFAULT!!NOTES | ||

| + | |- | ||

| + | |gain||comparator gain||-||1.0|| | ||

| + | |- | ||

| + | |} | ||

| + | |||

| + | ==Ideal Delay Block== | ||

| + | |||

| + | [[File:GL44.png]] | ||

| + | |||

| + | This model is an ideal signal delay block based on an ideal delay line model. | ||

| + | |||

| + | Parameters: | ||

| + | |||

| + | {| class="wikitable" | ||

| + | |- | ||

| + | !NAME!!PARAMETER!!UNITS!!DEFAULT!!NOTES | ||

| + | |- | ||

| + | |delay||time delay||sec||1u|| | ||

| + | |- | ||

| + | |} | ||

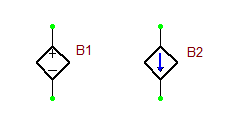

==Ideal Diode== | ==Ideal Diode== | ||

| Line 1,276: | Line 1,220: | ||

None | None | ||

| + | |||

| + | ==Ideal Full-Wave Rectifier Block== | ||

| + | |||

| + | [[File:GL47.png]] | ||

| + | |||

| + | This block rectifies an input signal at both positive and negative cycles with a default unity gain. | ||

| + | |||

| + | Parameters: | ||

| + | |||

| + | {| class="wikitable" | ||

| + | |- | ||

| + | !NAME!!PARAMETER!!UNITS!!DEFAULT!!NOTES | ||

| + | |- | ||

| + | |gain||rectifier gain||-||1.0|| | ||

| + | |- | ||

| + | |} | ||

| + | |||

| + | ==Ideal Gyrator Block== | ||

| + | |||

| + | [[File:GL48.png]] | ||

| + | |||

| + | An ideal gyrator is a linear two-port device which couples the current on one port to the voltage on the other and vice versa. The instantaneous voltages and currents instantaneous are related by: | ||

| + | |||

| + | :<math>v_{out}(t) = R \cdot i_{in}(t) </math> | ||

| + | |||

| + | :<math>v_{in}(t) = - R \cdot i_{out}(t) </math> | ||

| + | |||

| + | The ideal gyrator acts as an impedance inverter. | ||

| + | |||

| + | Parameters: | ||

| + | |||

| + | {| class="wikitable" | ||

| + | |- | ||

| + | !NAME!!PARAMETER!!UNITS!!DEFAULT!!NOTES | ||

| + | |- | ||

| + | |r||gyration resistance||Ω||1.0|| | ||

| + | |- | ||

| + | |} | ||

| + | |||

| + | ==Ideal Half-Wave Rectifier Block== | ||

| + | |||

| + | [[File:GL46.png]] | ||

| + | |||

| + | This block rectifies an input signal at positive cycles with a default unity gain. Its output at negative cycles is zero. | ||

| + | |||

| + | Parameters: | ||

| + | |||

| + | {| class="wikitable" | ||

| + | |- | ||

| + | !NAME!!PARAMETER!!UNITS!!DEFAULT!!NOTES | ||

| + | |- | ||

| + | |gain||rectifier gain||-||1.0|| | ||

| + | |- | ||

| + | |} | ||

==Ideal Operational Amplifier (Op-Amp)== | ==Ideal Operational Amplifier (Op-Amp)== | ||

| Line 1,290: | Line 1,288: | ||

|- | |- | ||

|A||open loop gain||-||50,000|| | |A||open loop gain||-||50,000|| | ||

| + | |- | ||

| + | |} | ||

| + | |||

| + | ==Ideal Phase Shifter Block== | ||

| + | |||

| + | [[File:GL45.png]] | ||

| + | |||

| + | This model is an ideal signal phase shifter block based on an ideal transmission line segment model. It is frequency-dependent and the signal phase shift is accurate only around the specified center frequency. | ||

| + | |||

| + | Parameters: | ||

| + | |||

| + | {| class="wikitable" | ||

| + | |- | ||

| + | !NAME!!PARAMETER!!UNITS!!DEFAULT!!NOTES | ||

| + | |- | ||

| + | |phi||phase shift||deg||90||must be positive | ||

| + | |- | ||

| + | |fo||center frequency||Hz||1Meg|| | ||

| + | |- | ||

| + | |} | ||

| + | |||

| + | ==Ideal Polarity Detector Block== | ||

| + | |||

| + | [[File:GL66.png]] | ||

| + | |||

| + | This 3-pin device measures the difference signal Δv = v<sub>pos</sub> - v<sub>neg</sub> and produces a binary output ±A according to the sign of Δv, where A is a user defined amplitude. | ||

| + | |||

| + | Parameters: | ||

| + | |||

| + | {| class="wikitable" | ||

| + | |- | ||

| + | !NAME!!PARAMETER!!UNITS!!DEFAULT!!NOTES | ||

| + | |- | ||

| + | |MaxVal||output amplitude||V||1|| | ||

| + | |- | ||

| + | |} | ||

| + | |||

| + | ==Ideal Splitter Block== | ||

| + | |||

| + | [[File:GL41.png]] | ||

| + | |||

| + | This model is an ideal signal splitter block with a default one-half split ratio. It splits the input signal by a ratio of k:(1-k). | ||

| + | |||

| + | Parameters: | ||

| + | |||

| + | {| class="wikitable" | ||

| + | |- | ||

| + | !NAME!!PARAMETER!!UNITS!!DEFAULT!!NOTES | ||

| + | |- | ||

| + | |k||split ratio||-||0.5|| | ||

|- | |- | ||

|} | |} | ||

| Line 1,302: | Line 1,350: | ||

where v<sub>P</sub>, i<sub>P</sub>, N<sub>P</sub> are the primary voltage, current and number of turns, respectively, and v<sub>S</sub>, i<sub>S</sub>, N<sub>S</sub> are the secondary voltage, current and number of turns, respectively. The red dots show the polarity of the windings on each side. This model has one parameter: ratio = n = N<sub>P</sub>/N<sub>S</sub>, which represents the primary-to-secondary turns ratio. Note that the ideal transformer model is defined based on controlled sources and does not involve any magnetic physical parameters as opposed to mutual inductors or ferrite core transformer. | where v<sub>P</sub>, i<sub>P</sub>, N<sub>P</sub> are the primary voltage, current and number of turns, respectively, and v<sub>S</sub>, i<sub>S</sub>, N<sub>S</sub> are the secondary voltage, current and number of turns, respectively. The red dots show the polarity of the windings on each side. This model has one parameter: ratio = n = N<sub>P</sub>/N<sub>S</sub>, which represents the primary-to-secondary turns ratio. Note that the ideal transformer model is defined based on controlled sources and does not involve any magnetic physical parameters as opposed to mutual inductors or ferrite core transformer. | ||

| + | |||

| + | == Impulse Generator == | ||

| + | |||

| + | [[File:GL19.png]] | ||

| + | |||

| + | This is a voltage source that generates a periodic impulse train with oscillating between zero and a user defined maximum voltage level. | ||

| + | |||

| + | Parameters: | ||

| + | |||

| + | {| class="wikitable" | ||

| + | |- | ||

| + | !NAME!!PARAMETER!!UNIT!!DEFAULT!!NOTES | ||

| + | |- | ||

| + | |T||impulse period||sec||1u||required | ||

| + | |- | ||

| + | |duty_cycle||impulse duty cycle||-||0.01||required | ||

| + | |- | ||

| + | |max_val||maximum output voltage level||V||1|| | ||

| + | |- | ||

| + | |delay||delay time||sec||0|| | ||

| + | |- | ||

| + | |} | ||

==Inductance Meter== | ==Inductance Meter== | ||

| Line 1,449: | Line 1,519: | ||

|- | |- | ||

|cjo||diode junction capacitance||F||1n|| | |cjo||diode junction capacitance||F||1n|| | ||

| + | |- | ||

| + | |} | ||

| + | |||

| + | == Integer Modulo Block == | ||

| + | |||

| + | [[File:GL58.png]] | ||

| + | |||

| + | This 3-pin device requires a voltage with an integer value on its second input pin. It produces a voltage equal to v<sub>in1</sub> % v<sub>in2</sub> and sends it to the output with a default unity gain. | ||

| + | |||

| + | Parameters: | ||

| + | |||

| + | {| class="wikitable" | ||

| + | |- | ||

| + | !NAME!!PARAMETER!!UNITS!!DEFAULT!!NOTES | ||

| + | |- | ||

| + | |gain||gain||-||1.0|| | ||

| + | |- | ||

| + | |} | ||

| + | |||

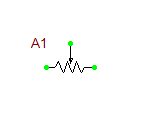

| + | ==Integrator Block== | ||

| + | |||

| + | [[File:G32.png]] | ||

| + | |||

| + | The Integrator Gain and input offset parameters are also included to allow for tailoring of the required | ||

| + | signa. Output upper and lower limits are also included to prevent convergence errors resulting from excessively | ||

| + | large output values. Note that these limits specify integrator behavior similar to that found in an operational | ||

| + | amplifier-based integration stage, in that once a limit is reached, additional storage does not occur. | ||

| + | Thus the input of a negative value to an integrator which is currently driving at the out_upper_limit | ||

| + | level will immediately cause a drop in the output, regardless of how long the integrator was previously | ||

| + | summing positive inputs. The incremental value of output below the output_upper_limit and above the output_lower_limit | ||

| + | at which smoothing begins is specified via the limit_range parameter. In AC analysis, the value returned | ||

| + | is equal to the gain divided by the radian frequency of analysis. | ||

| + | |||

| + | Note that truncation error checking is included in the \93int\94 block. This should provide for a more accurate | ||

| + | simulation for the time integration function, since the model will inherently request smaller time increments | ||

| + | between simulation points if truncation errors would otherwise be excessive. | ||

| + | |||

| + | Model Identifier: int | ||

| + | |||

| + | Netlist Format: | ||

| + | |||

| + | A<device_name> <in_pin> <out_pin> <model_name> | ||

| + | |||

| + | .model <model_name> int out_lower_limit = <value> out_upper_limit = <value> {<param1 = value> < param2 = value> ...} | ||

| + | |||

| + | Example: | ||

| + | |||

| + | A1 1 2 integrator_block | ||

| + | |||

| + | .model integrator_block int out_lower_limit = -1t out_upper_limit = 1t | ||

| + | |||

| + | Parameters: | ||

| + | |||

| + | {| class="wikitable" | ||

| + | |- | ||

| + | !NAME!!PARAMETER!!UNITS!!DEFAULT!!NOTES | ||

| + | |- | ||

| + | |gain||gain||-||1.0|| | ||

| + | |- | ||

| + | |in_offset||output offset||V||0.0|| | ||

| + | |- | ||

| + | |out_lower_limit||output lower limit||V||-1t||required | ||

| + | |- | ||

| + | |out_upper_limit||output upper limit||V||1t||required | ||

| + | |- | ||

| + | |limit_range||upper and lower limit smoothing range||-||1.0e-6|| | ||

| + | |- | ||

| + | |out_ic||output initial condition||V||0.0|| | ||

|- | |- | ||

|} | |} | ||

| Line 1,457: | Line 1,595: | ||

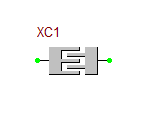

This device is an interactive switch that can be closed or opened either directly from the Schematic Editor by clicking on its symbol or from the Instrument Panel. | This device is an interactive switch that can be closed or opened either directly from the Schematic Editor by clicking on its symbol or from the Instrument Panel. | ||

| + | |||

| + | ==Interdigital Capacitor== | ||

| + | [[File:G97.png]] | ||

| + | |||

| + | This is a four-pin, two-port device that models a planar interdigital capacitor. | ||

| + | |||

| + | Model Identifier: interdigital | ||

| + | |||

| + | Parameters: | ||

| + | |||

| + | {| class="wikitable" | ||

| + | |- | ||

| + | !NAME!!PARAMETER!!UNITS!!DEFAULT!!NOTES | ||

| + | |- | ||

| + | |w||finger strip width||mm||0.1|| | ||

| + | |- | ||

| + | |s||finger strip spacing||mm||0.1|| | ||

| + | |- | ||

| + | |N||number of fingers||-||5|| | ||

| + | |- | ||

| + | |l||capacitor length||mm||1.0|| | ||

| + | |- | ||

| + | |h||substrate thickness||mm||1.6|| | ||

| + | |- | ||

| + | |er||substrate relative permittivity||-||2.2|| | ||

| + | |- | ||

| + | |} | ||

| + | |||

| + | ==Inverted Microstrip Line== | ||

| + | [[File:GK62.png]] | ||

| + | |||

| + | This is a four-pin, two-port device that models an inverted microstrip line segment on a single-layer dielectric slab/substrate placed at a specified height above a ground plane. | ||

| + | |||

| + | Model Identifier: microstrip-inverted | ||

| + | |||

| + | Parameters: | ||

| + | |||

| + | {| class="wikitable" | ||

| + | |- | ||

| + | !NAME!!PARAMETER!!UNITS!!DEFAULT!!NOTES | ||

| + | |- | ||

| + | |w||microstrip width||mm||4.8|| | ||

| + | |- | ||

| + | |h||substrate thickness||mm||1.6|| | ||

| + | |- | ||

| + | |er||substrate relative permittivity||-||2.2|| | ||

| + | |- | ||

| + | |b||microstrip height above ground||mm||1.6|| | ||

| + | |- | ||

| + | |len||microstrip length||m||10|| | ||

| + | |- | ||

| + | |} | ||

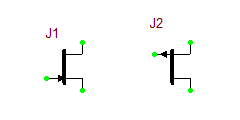

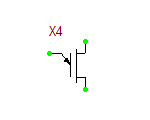

==Junction Field Effect Transistor (JFET)== | ==Junction Field Effect Transistor (JFET)== | ||

Latest revision as of 16:14, 7 October 2024

Contents

- 1 4-Bit ADC Bridge

- 2 4-Bit DAC Bridge

- 3 AC/RF Current Source

- 4 AC/RF Voltage Source

- 5 Alternate Ferrite Core Transformer

- 6 Alternate Ideal Transformer

- 7 AM Modulated Source

- 8 Analog Clock

- 9 Analog-to-Digital Converter (ADC) Bridge

- 10 Arbitrary Temporal Waveform Generator

- 11 Auto-Transformer

- 12 Bipolar Junction Transistor (BJT)

- 13 Capacitance Meter

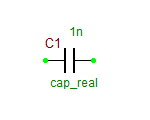

- 14 Capacitor

- 15 Center-Tapped Ferrite Core Transformer

- 16 Controlled Sine Wave Oscillator

- 17 Controlled Sources

- 18 Controlled Square Wave Oscillator

- 19 Controlled Triangle Wave Oscillator

- 20 Crystal

- 21 Current Noise Source

- 22 Current Source

- 23 Current-Controlled Switch

- 24 Darlington Pair

- 25 D Flip-Flop

- 26 D Latch

- 27 DC Bias Sources Vcc, Vee, Vdd, Vss

- 28 Digital-to-Analog Converter (DAC) Bridge

- 29 Diode

- 30 Diode Bridge

- 31 Doubly Center-Tapped Ferrite Core Transformer

- 32 DPDT Switch

- 33 DPST Switch

- 34 Ferrite Core Transformer

- 35 FM Modulated Source

- 36 Frequency Meter

- 37 Fuse

- 38 Ground

- 39 Hysteresis Block (XSPICE)

- 40 Ideal Buffer Block

- 41 Ideal Center-Tapped Transformer with Push-Pull Input

- 42 Ideal Center-Tapped Transformer with Push-Pull Output

- 43 Ideal Comparator Block

- 44 Ideal Delay Block

- 45 Ideal Diode

- 46 Ideal Full-Wave Rectifier Block

- 47 Ideal Gyrator Block

- 48 Ideal Half-Wave Rectifier Block

- 49 Ideal Operational Amplifier (Op-Amp)

- 50 Ideal Phase Shifter Block

- 51 Ideal Polarity Detector Block

- 52 Ideal Splitter Block

- 53 Ideal Transformer

- 54 Impulse Generator

- 55 Inductance Meter

- 56 Inductive Coupler Block

- 57 Inductive Coupling (XSPICE)

- 58 Inductor

- 59 Inductor with Ferrite Core

- 60 Insulated Gate Bipolar Transistor (IGBT)

- 61 Integer Modulo Block

- 62 Integrator Block

- 63 Interactive Switch

- 64 Interdigital Capacitor

- 65 Inverted Microstrip Line

- 66 Junction Field Effect Transistor (JFET)

- 67 Light Emitting Diode (LED)

- 68 Linear Current-Controlled Current Source (CCCS)

- 69 Linear Current-Controlled Voltage Source (CCVS)

- 70 Linear Voltage-Controlled Current Source (VCCS)

- 71 Linear Voltage-Controlled Voltage Source (VCVS)

- 72 Lossless Transmission Line

- 73 Lossy Transmission Line

- 74 Magnetic Core (XSPICE)

- 75 Marker

- 76 MESFET

- 77 MOSFET

- 78 Mutual Inductors

- 79 Non-Ideal Current Transformer

- 80 Non-Ideal Diode

- 81 Non-Ideal Voltage Transformer

- 82 Nonlinear Capacitor

- 83 Nonlinear Conductor

- 84 Nonlinear Dependent Sources

- 85 Nonlinear Inductor

- 86 Nonlinear Resistor

- 87 Operational Amplifier (Op-Amp)

- 88 Optocoupler

- 89 Overtone Crystal

- 90 Photodiode

- 91 Piecewise Linear (PWL) Controlled Source

- 92 PM Modulated Source

- 93 Potentiometer

- 94 Programmable Unijunction Transistor (PUT)

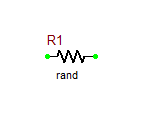

- 95 Random Resistor

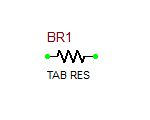

- 96 Real Capacitor

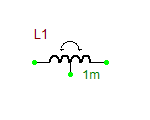

- 97 Real Inductor

- 98 Real Resistor

- 99 Resistor

- 100 Schottky Diode

- 101 Semiconducting Capacitor

- 102 Semiconductor Resistor

- 103 Silicon-Controlled Rectifier (SCR)

- 104 SPDT Switch

- 105 SPST Switch

- 106 Tabulated Conductor

- 107 Tabulated Resistor

- 108 Tapped Inductor

- 109 Temperature-Dependent Current Source

- 110 Temperature-Dependent Voltage Source

- 111 Thermometer

- 112 Triac Thyristor

- 113 Uniform RC Transmission Line

- 114 Varactor Diode

- 115 Voltage-Controlled Capacitor

- 116 Voltage-Controlled Inductor

- 117 Voltage-Controlled Resistor

- 118 Voltage-Controlled Switch

- 119 Voltage Noise Source

- 120 Voltage Source

- 121 XSpice Devices and their models

- 122 Zener Diode

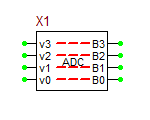

4-Bit ADC Bridge

This 8-pin device is simply a bundle of 4 1-bit ADC bridges. Each analog input pin has a corresponding digital output pin.

Parameters:

| NAME | PARAMETER | UNIT | DEFAULT | NOTES |

|---|---|---|---|---|

| in_low | maximum 0-valued analog input | V | 0.1 | required |

| in_high | minimum 1-valued analog input | V | 0.9 | required |

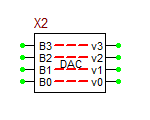

4-Bit DAC Bridge

This 8-pin device is simply a bundle of 4 1-bit DAC bridges. Each digital input pin has a corresponding analog output pin.

Parameters:

| NAME | PARAMETER | UNIT | DEFAULT | NOTES |

|---|---|---|---|---|

| out_low | analog output for 0 digital input | V | 0 | required |

| out_high | analog output for 1 digital input | V | 1 | required |

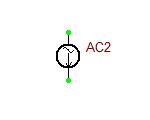

AC/RF Current Source

This is a simplified version of the standard Current Source, in which the AC "Use" box has been checked by default. Therefore, it is ready to be used for AC frequency sweep. Note that for AC frequency sweep, you do not need to specify the frequency.

Parameters:

| NAME | PARAMETER | UNIT | DEFAULT | NOTES |

|---|---|---|---|---|

| VA | peak current amplitude | A | 1 | required |

| Freq | frequency | Hz | 1 | required |

| Phase | phase | deg | 0 | |

| offset | DC offset for small-signal current | A | 0 |

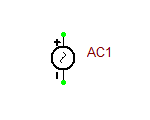

AC/RF Voltage Source

This is a simplified version of the standard Voltage Source, in which the AC "Use" box has been checked by default. Therefore, it is ready to be used for AC frequency sweep. Note that for AC frequency sweep, you do not need to specify the frequency.

Parameters:

| NAME | PARAMETER | UNIT | DEFAULT | NOTES |

|---|---|---|---|---|

| VA | peak voltage amplitude | V | 1 | required |

| Freq | frequency | Hz | 1 | required |

| Phase | phase | deg | 0 | |

| offset | DC offset for small-signal voltage | V | 0 |

Alternate Ferrite Core Transformer

The alternate ferrite core transformer is a four-pin two-port device, which has the same behavior as the Ferrite Core Transformer, except for the reversed polarity of its secondary port.

Alternate Ideal Transformer

The alternate ideal transformer is a four-pin two-port device, which has the same behavior as the Ideal Transformer, except for the reversed polarity of its secondary port.

AM Modulated Source

This is a voltage source with a single-tone amplitude modulated waveform. The AM modulation index MDI is defined as the ratio of maximum amplitude deviation to maximum signal amplitude.

Parameters:

| NAME | PARAMETER | UNIT | DEFAULT | NOTES |

|---|---|---|---|---|

| V0 | offset | V | 0 | |

| VA | amplitude | V | 1 | |

| FC | carrier frequency | Hz | 1 | required |

| MDI | modulation index | - | 0 | required |

| FS | signal frequency | Hz | 1 | required |

Analog Clock

This is a periodic pulse generator with a default 0V low output level and a default 5V high output level.

Parameters:

| NAME | PARAMETER | UNIT | DEFAULT | NOTES |

|---|---|---|---|---|

| delay | delay time | sec | 0 | |

| rise | rise time | sec | 0.1n | |

| fall | fall time | sec | 0.1n | |

| pulse_wid | clock pulse width | sec | 1u | required |

| period | clock period | - | 2u | required |

| out_low | low output voltage level | V | 0 | |

| out_high | high output voltage level | V | 5 |

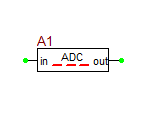

Analog-to-Digital Converter (ADC) Bridge

The ADC Bridge takes an analog value from an analog node and may be in the form of a voltage or current. If the input is less than or equal to "in_low", then a digital "0" is generated. If the input is greater than or equal to "in_high", a digital "1" is generated. Otherwise, a digital "UNKNOWN" is the output value. Unlike the DAC Bridge, ramping or delay is not applicable. Rather, the continuous ramping of the input provides for any associated delays in the digitized signal.

This model also posts an input load value based on the parameter input_load.

Model Identifier: adc_bridge

Netlist Format:

A<device_name> [<in_pin> {<in2_pin>> ...}] [<out_pin> {<out2_pin> ...}] <model_name>

.model <model_name> adc_bridge {<param1 = value> < param2 = value> ...}

Example:

A [1] [2] adc_bridge

.model adc_bridge adc_bridge in_low = .1 fall_delay = 1n

Parameters:

| NAME | PARAMETER | UNIT | DEFAULT | NOTES |

|---|---|---|---|---|

| in_low | maximum 0-valued analog input | V | 0.1 | required |

| in_high | minimum 1-valued analog input | V | 0.9 | required |

| rise_delay | L-to-H delay time | sec | 1n | |

| fall_delay | H-to-L delay time | sec | 1n |

Arbitrary Temporal Waveform Generator

This is a voltage source with an arbitrary waveform defined by a mathematical expression. You have to open the subcircuit model dialog by clicking the View Subcircuit button and edit its text. Enter any mathematical expression in the variable "v(t)" standing for time.

Examples:

- v(t) is equivalent to f(t) = t.

- 0.1*(v(t))^2 is equivalent to f(t) = 0.1t^2.

- sin(2*pi*v(t)) is equivalent to f(t) = sin(2πt).

Parameters:

| NAME | PARAMETER | UNIT | DEFAULT | NOTES |

|---|---|---|---|---|

| Tmax | maximum signal duration | sec | 1e6 | required |

Auto-Transformer

This 3-pin device models an auto-transformer with mutual coupling effect.

Parameters:

| NAME | PARAMETER | UNIT | DEFAULT | NOTES |

|---|---|---|---|---|

| Lp | primary inductance | H | 1m | |

| Ls | secondary inductance | H | 1m | |

| k | coefficient of coupling | - | 1.0 |

Bipolar Junction Transistor (BJT)

The BJT is an active device which has up to 4 pins. The three standard pins are base, emitter, and collector. These are given in the default symbol. The substrate, which is grounded by default, is the fourth pin. To use the BJT with the substrate, create a new 4-pin BJT using the Device Editor and Symbol Editor.

The standard device parameters are AREA, OFF, IC, and T. They are described below:

| AREA | area factor (optional) (If not specified, the default value is 1.0.) |

| OFF | initial condition for the DC analysis (optional) |

| IC | initial condition (optional) (Used when a transient analysis is desired, which starts from other than the quiescent operating point.) |

| T | operating temperature of the device (optional) |

Area factor scales the model parameters RE and RC. IC VBE is the initial voltage from base emitter. IC VCE is the initial voltage from collector to emitter. TEMP is the overriding temperature. These parameters are based on the Gummel and Poon integral-charge model. If these parameters are not specified, then it will reduce to the simpler Ebers-Moll model.

The process model is mandatory for the BJT. Descriptions of the process model parameters are given in the following table:

| NAME | PARAMETER | UNITS | DEFAULT | EXAMPLE |

|---|---|---|---|---|

| IS | transport saturation current | A | 1.0e-16 | 1.0e-15 |

| BF | ideal maximum forward beta | 100 | 100 | |

| NF | forward current emission coefficient | 1.0 | 1 | |

| VAF | forward Early voltage | V | infinite | 200 |

| IKF | corner forward beta high current roll-off | A | infinite | 0.01 |

| ISE | B-E leakage saturation current | A | 0 | 1.0e-13 |

| NE | B-E leakage emission coefficient | 1.5 | 2 | |

| BR | ideal maximum reverse beta | 1 | 0.1 | |

| NR | reverse current emission coefficient | 1 | 1 | |

| VAR | reverse Early voltage | V | infinite | 200 |

| IKR | corner reverse beta high current roll-off | A | infinite | 0.01 |

| ISC | B-C leakage saturation current | A | 0 | 1.0e-13 |

| NC | B-C leakage emission coefficient | 2 | 1.5 | |

| RB | zero bias base resistance | ohms | 0 | 100 |

| IRB | current where base resistance falls halfway to minimum value | A | infinite | 0.1 |

| RBM | minimum base resistance at high currents | ohms | RB | 10 |

| RE | emitter resistance | ohms | 0 | 1 |

| RC | collector resistance | ohms | 0 | 10 |

| CJE | B-E zero bias depletion capacitance | F | 0 | 2pF |

| VJE | B-E built-in potential | V | 0.75 | 0.6 |

| MJE | B-E junction exponential factor | 0.33 | 0.33 | |

| TF | ideal forward transit time | sec | 0 | 0.1ns |

| XTF | coefficient for bias dependence of TF | 0 | ||

| VTF | voltage describing VBC dependence of TF | V | infinite | |

| ITF | high-current parameter for effect on TF | A | 0 | |

| PTF | excess phase at freq=1.0/(TF*2PI)Hz | degree | 0 | |

| CJC | B-C zero bias depletion capacitance | F | 0 | 2pF |

| VJC | B-C built-in potential | V | 0.75 | 0.5 |

| MJC | B-C junction exponential factor | 0.33 | 0.5 | |

| XCJC | fraction of B-C depletion capacitance connected to internal base node | 1 | ||

| TR | ideal reverse transit time | sec | 0 | 10ns |

| CJS | zero bias collector-substrate capacitance | F | 0 | 2pF |

| VJS | substrate junction built-in potential | V | 0.75 | |

| MJS | substrate junction exponential factor | 0 | 0.5 | |

| XTB | forward and reverse beta temp. exponent | 0 | ||

| EG | energy gap for temperature effect on IS | eV | 1.11 | |

| XTI | temperature exponent for effect on IS | 3 | ||

| KF | flicker-noise coefficient | 0 | ||

| AF | flicker-noise exponent | 1 | ||

| FC | coefficient for forward bias depletion capacitance formula | 0.5 | ||

| TNOM | parameter measurement temperature | deg. C | 27 | 50 |

Capacitance Meter

The Capacitance Meter measures the total capacitance between a circuit node and the ground. The input pin of the device is connected to the measurement node. The output voltage of the device is then a scaled value equal to the total capacitance seen on its input multiplied by the gain parameter. This model is primarily intended as a building block for other models which must sense a capacitance value and alter their behavior based upon it.

Model Identifier: cmeter

Netlist Format:

A<device_name> <in_pin> <out_pin> <model_name>

.model <model_name> cmeter {<gain = value>}

Example:

A1 1 2 cap_meter

.model cap_meter cmeter gain = 1

Parameters:

The only parameter is the gain with a default value of 1.0.

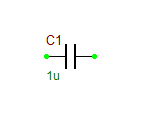

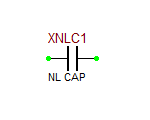

Capacitor

Capacitors are used to store electrical energy. They can filter or remove AC signals or block DC current without disrupting AC signals. A capacitor's ability to store energy is termed capacitance and is measured in Farads, with values from pF to mF. The only time current flows through a capacitor is when the charge is collected on, or is removed from, its parallel plates. This means that the voltage across the capacitor is changing, which doesn't conform to DC analysis. In a physical circuit, there is a transition stage during which capacitors charge up to their final values. The result is the same as if these capacitors did not exist and the connections to them were left dangling. In other words, in a (steady-state) DC analysis, a capacitor behaves like an open circuit. Therefore, it is important that no section of the circuit is isolated from the capacitors. Every circuit node needs some path for DC current to the ground.

A capacitor's transient behavior is described by the equation:

i(t) = C * (dv(t)/dt)

Its initial voltage is only important when the simulator performs a transient analysis, and the "Use Initial Conditions" checkbox is checked.

An capacitor's AC behavior is described by the equation:

i = j ω * C * v

All capacitor names must begin with C.

Netlist Format:

C<device_name> <N+> <N-> <value>

Example:

C1 1 2 10p

RF.Spice A/D provides three types of capacitors: simple, user-defined (or real) and semiconductor. The standard capacitor parameters are N+, N-, VALUE, and IC. In a simple capacitor, VALUE must be specified for the capacitance in Farads. IC is the (optional) initial condition for the capacitor voltage.

Center-Tapped Ferrite Core Transformer

This five-pin three-port device models a center-tapped physical transformer with a magnetic ferrite core. Its model is based on XSPICE's magnetic core and inductive coupling models. For this device you need to specify physical parameters like cross sectional area, core length and number of primary and secondary turns. The physical model of the magnetic device is defined by two vectors: magnetic field intensity H in A/m and magnetic flux density B (also known as magnetic induction) in Tesla. The default array values are:

H_array = [-250 -100 -50 -37.5 -25 -12.5 0 12.5 25 37.5 50 100 250]

B_array = [-0.375 -0.36 -0.32 -0.29 -0.24 -0.15 0 0.15 0.24 0.29 0.32 0.36 0.375]

To change the value of H/B arrays, open the subcircuit model dialog by clicking the View Subcircuit button and edit its text.

Parameters:

| NAME | PARAMETER | UNITS | DEFAULT | NOTES |

|---|---|---|---|---|

| n_prim | number of primary inductor coupling turns | - | 100 | required |

| n_sec | number of full-winding secondary inductor coupling turns | - | 100 | required |

| area | cross-sectional area | m2 | 1e-5 | |

| length | core length | m | 0.01 |

Controlled Sine Wave Oscillator

This is a four-terminal function generator with a sinusoidal wave output, whose frequency is controlled by an input voltage. The functional dependency of the output frequency on the input voltage is piecewise linear and is defined as a two-dimensional table similar to a piecewise linear (PWL) controlled source. In the "frequency vs. voltage" curve, the array "cntl_array" defines voltage values in Volts and the array "freq_array" defines the corresponding frequencies in Hz. This function has parameterizable values of low and high peak output voltage.

Model Identifier: sine

Netlist Form:

A<device_name> %vd(<cntl_in_pin> <cntl_in_ref_pin>) %vd(<out_pin> <out_ref_pin>) <model_name>

.model <model_name> sine cntl_array = [<value1> <value2>] freq_array = [<value1> <value2>] {<param1 = value> < param2 = value> ...}

Example:

A1 %vd(1 3) %vd(2 4) sine

.model sine sine cntl_array = [0 1] freq_array = [1 1000]

Parameters:

| NAME | PARAMETER | UNIT | DEFAULT | NOTES |

|---|---|---|---|---|

| Cntl_array | control array | V | [0 1] | required |

| Freq_array | frequency array | Hz | [1 1000] | required |

| Out_low | output peak low value | V | -1.0 | |

| Out_high | output peak high value | V | 1.0 |

Controlled Sources

Circuits can contain linear dependent sources characterized by one of the following equations (where g, e, f, and h are constants representing transconductance, voltage gain, current gain, and transresistance, respectively):

iout = g vin vout = e vin iout = f iin vout = h iin

For further information, refer to:

Linear Current Controlled Current Source (CCCS)

Linear Voltage Controlled Current Source (VCCS)

Linear Current Controlled Voltage Source (CCVS)

Linear Voltage Controlled Voltage Source (VCVS)

Controlled Square Wave Oscillator

This is a four-terminal function generator with a square wave output, whose frequency is controlled by an input voltage. The functional dependency of the output frequency on the input voltage is piecewise linear and is defined as a two-dimensional table similar to a piecewise linear (PWL) controlled source. In the "frequency vs. voltage" curve, the array "cntl_array" defines voltage values in Volts and the array "freq_array" defines the corresponding frequencies in Hz.

Model Identifier: square

Netlist Format:

A<device_name> %vd(<cntl_in_pin> <cntl_in_ref_pin>) %vd(<out_pin> <out_ref_pin>) <model_name>

.model <model_name> square cntl_array = [<value1> <value2>] freq_array = [<value1> <value2>] {<param1 = value> < param2 = value> ...}

Example:

A1 %vd(1 3) %vd(2 4) square

.model square square cntl_array = [0 1] freq_array = [1 1000]

Parameters:

| NAME | PARAMETER | UNIT | DEFAULT | NOTES |

|---|---|---|---|---|

| Cntl_array | control array | V | [0 1] | required |

| Freq_array | frequency array | Hz | [0 1000] | required |

| Out_low | output peak low value | V | -1.0 | |

| Out_high | output peak high value | V | 1.0 | |

| Duty_cycle | Duty cycle | - | 0.5 | |

| Rise_time | Output rise time | sec | 1.0e-9 | |

| Fall_time | Output fall time | sec | 1.0e-9 |

Controlled Triangle Wave Oscillator

This is a four-terminal function generator with a triangle wave output, whose frequency is controlled by an input voltage. The functional dependency of the output frequency on the input voltage is piecewise linear and is defined as a two-dimensional table similar to a piecewise linear (PWL) controlled source. In the "frequency vs. voltage" curve, the array "cntl_array" defined voltage values in Volts and the array "freq_array" defines the corresponding frequencies in Hz.

Model Identifier: triangle

Netlist Format:

A<device_name> %vd(<cntl_in_pin> <cntl_in_ref_pin>) %vd(<out_pin> <out_ref_pin>) <model_name>

.model <model_name> tirangle cntl_array = [<value1> <value2>] freq_array = [<value1> <value2>]{<param1 = value> < param2 = value> ...}

Example:

A1 %vd(1 4) %vd(2 3) triangle

.model triangle triangle cntl_array = [0 1] freq_array = [1 1000]

Parameters:

| NAME | PARAMETER | UNIT | DEFAULT | NOTES |

|---|---|---|---|---|

| Cntl_array | control array | V | [0 1] | required |

| Freq_array | frequency array | Hz | [0 1000] | required |

| Out_low | output peak low value | V | -1.0 | |

| Out_high | output peak high value | V | 1.0 | |

| Rise_duty | Rise time duty cycle | 0.5 |

Crystal

This is a 2-pin parameterized crystal device.

Parameters:

| NAME | PARAMETER | UNITS | DEFAULT | NOTES |

|---|---|---|---|---|

| CM | motional capacitance | F | 10f | |

| C0 | shunt capacitance | F | 1p | |

| RM | motional resistance | Ohms | 100 | |

| LM | motional inductance | H | 100m |

Current Noise Source

This is a current noise generator characterized by a spectral density and corner frequency. You have to click the Edit Model... button to access the parameters of this device.

Parameters:

| NAME | PARAMETER | UNIT | DEFAULT | NOTES |

|---|---|---|---|---|

| En | noise current | A/√Hz | 1p | required |

| freq | noise corner frequency | Hz | 100 | required |

Current Source

Current source has a DC value, a transient behavior, an AC behavior, and distortion parameters. The transient type, AC parameters, and distortion parameters are defined on the first tab of the source's property dialog. The transient expression can be a pulse, sinusoid, exponential, or piecewise linear. The DC value of a current source is its initial transient value. For a source with a sinusoidal transient behavior, for example, the DC value will be equal to its transient offset current. The AC parameters are magnitude and phase. These are used during the AC Frequency Sweep analysis. The distortion parameters, two sets of magnitude and phase, are used during the distortion analysis. The AC and distortion parameters are defined on the second tab of the source's property dialog.

Current-Controlled Switch

Switches are devices that exhibit high resistance when open (OFF state) and low resistance when closed (ON state). The switch model allows an almost ideal switch to be specified. With careful selection of the on and off resistances, they can effectively represent zero and infinite resistances in comparison to other circuit elements, while sustaining the model condition of a positive, finite value.

There are two versions of Current-Controlled Switch: two-terminal and four-terminal. For the two-terminal device, you must specify the name of the controlling Ammeter or voltage source, as well as the turn-on and turn-off currents in Amperes and on and off resistance values in Ohms. The four-terminal device already provides nodes for a controlling ammeter, and you just specify the rest of parameters. When the current through the switch or controlling device is greater or equal to the turn-on current, the switch closes. When the current through the switch or controlling device is less than or equal to the turn off current, the switch opens.

| NAME | PARAMETER | UNITS | DEFAULT | NOTES |

|---|---|---|---|---|

| I_ON | turn-on current | A | 0.0 | |

| I_OFF | turn-off current | A | 0.0 | |

| RON | closed resistance | Ohms | 1.0 | |

| ROFF | open resistance | Ohms | 1/GMIN |

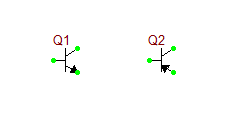

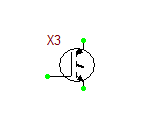

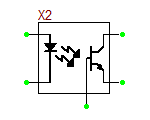

Darlington Pair

A Darlington pair is a three-pin device that consists of two interconnected BJT transistors of the same type. The collectors of two transistors are connected together to provide the "Collector" pin of the pair. The base of the first BJT acts the "Base" pin of the pair. The emitter of the first BJT is internally connected to the base of the second BJT. The emitter of the second BJT acts as the "Emitter" pin of the pair. There are two types of Darlington pair: NPN and PNP. The parameterized generic Darlington pair also contains a diode connected between the collector and emitter pin as well as two base-emitter resistors, one across each BJT.

Parameters:

| NAME | PARAMETER | UNITS | DEFAULT | NOTES |

|---|---|---|---|---|

| is_bjt | bjt saturation current | A | 1.0e-12 | |

| bf_bjt | bjt forward beta | - | 150 | |

| nf_bjt | bjt forward emission coefficient | - | 1 | |

| ise_bjt | B-E leakage saturation current | A | 0 | |

| ne_bjt | B-E leakage emission coefficient | - | 1 | |

| br_bjt | ideal maximum reverse beta | - | 1 | |

| nr_bjt | reverse current emission coefficient | - | 1 | |

| isc_bjt | B-C leakage saturation current | A | 0 | |

| nc_bjt | B-C leakage emission coefficient | - | 1 | |

| rb_bjt | zero bias base resistance | Ohms | 0 | |

| irb_bjt | current where base resistance falls halfway to minimum value | A | inf | |

| rbm_bjt | minimum base resistance at high currents | ohms | 0 | |

| re_bjt | emitter resistance | Ohms | 0 | |

| rc_bjt | collector resistance | Ohms | 0 | |

| cje_bjt | B-E zero bias depletion capacitance | F | 0 | |

| vje_bjt | B-E built-in potential | V | 0.75 | |

| mje_bjt | B-E junction grading coefficient | - | 0.33 | |

| cjc_bjt | B-C zero bias depletion capacitance | F | 0 | |

| vjc_bjt | B-C built-in potential | V | 0.75 | |

| mjc_bjt | B-C junction exponential factor | - | 0.33 | |

| tf_bjt | ideal forward transit time | sec | 0 | |

| tr_bjt | ideal reverse transit time | sec | 0 | |

| is_d | diode saturation current | A | 1.0e-12 | |

| rs_d | diode resistance | Ohms | 0 | |

| n_d | diode emission coefficient | - | 1 | |

| cjo_d | diode junction capacitance | F | 0 | |

| vj_d | diode junction potential | V | 1 | |

| m_d | diode grading coefficient | 0.5 | ||

| tnom | parameter measurement temperature | deg C | 27 | |

| r1 | first base-emitter resistance | Ohms | 1k | |

| r2 | second base-emitter resistance | Ohms | 1k |

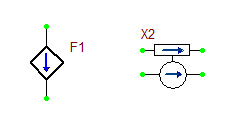

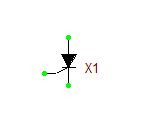

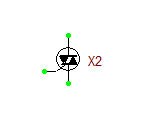

D Flip-Flop

The digital D-type flip-flop is a one-bit, edge-triggered storage element which stores data whenever the clock (CLK) input line transitions from 0 (low) to 1 (high). In addition, there are asynchronous set and reset signals, which are independent of the clock. When SET = RESET = 0, the data on the D line is transferred to the output Q on the rising edge of the clock. The combination SET = 1 and RESET = 0, causes Q = 1. The combination SET = 0 and RESET = 1 causes Q = 0. The combination SET = RESET = 1 is illegal and is resolved by setting both outputs Q and Q_bar to 1.

Truth Table:

|

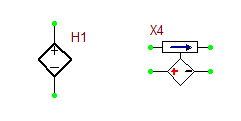

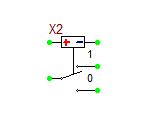

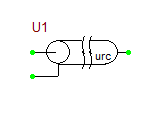

D Latch

The digital D-type latch is a one-bit, level-sensitive storage element which outputs the value on the data (D) line whenever the enable (EN) input line is 1 (high). The value on the data line is stored, i.e., held on the output (Q) line whenever the enable (EN) line is 0 (low). In addition, there are set and reset signals, which are independent of the enable line. When SET = RESET = 0, the data on the D line is transferred to the output Q whenever EN = 1. The combination SET = 1 and RESET = 0, causes Q = 1. The combination SET = 0 and RESET = 1 causes Q = 0. The combination SET = RESET = 1 is illegal and is resolved by setting both outputs Q and Q_bar to 1.

Truth Table:

|

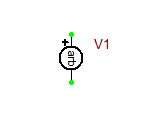

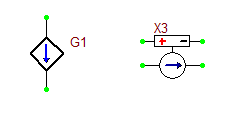

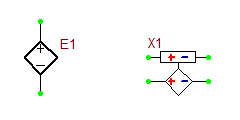

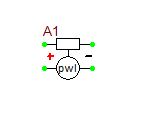

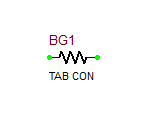

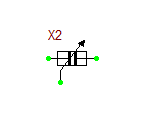

DC Bias Sources Vcc, Vee, Vdd, Vss

These are simple 1-pin DC voltage sources. Vcc and Vdd provide a positive voltage, while Vee and Vss provide a negative voltage

Parameters:

| NAME | PARAMETER | UNIT | DEFAULT | NOTES |

|---|---|---|---|---|

| vcc | bias voltage | V | +15 | required |

| vee | bias voltage | V | -15 | required |

| vdd | bias voltage | V | +15 | required |

| vss | bias voltage | V | -15 | required |

Digital-to-Analog Converter (DAC) Bridge

The DAC Bridge takes a digital value from a digital node and can only be eiter "0", "1", or "U". It then outputs the value "out_low", "out_high" or "out_udndef", or ramps linearly toward one of these "final" values from its curent analog output level. This ramping speed depends on the values of "t_rise" and "t_fall".

Model Identifier: dac_bridge

Netlist Format:

A<device_name> [<in_pin> {<in2_pin>> ...}] [<out_pin> {<out2_pin> ...}] <model_name>

.model <model_name> dac_bridge {<param1 = value> < param2 = value> ...}

Example:

A [1] [2] dac_bridge

.model dac_bridge dac_bridge out_low = 0 fall_delay = 1n

Parameters:

| NAME | PARAMETER | UNIT | DEFAULT | NOTES |

|---|---|---|---|---|

| out_low | analog output for 0 digital input | V | 0 | required |

| out_high | analog output for 1 digital input | V | 1 | required |

| out_undef | analog output for undefined digital input | V | 0.5 | required |

| input_load | capacitive input load | F | 1p | |

| t_rise | L-to-H delay time | sec | 1n | |

| t_fall | H-to-L delay time | sec | 1n |

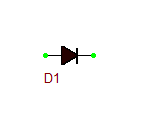

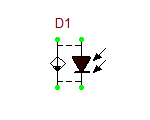

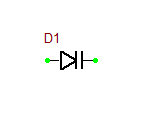

Diode

Diodes allow current flow only in one direction, following their symbol's arrow, and thus can be used as simple solid state switches in AC circuits.

The standard device parameters are AREA, OFF, IC, and T. They are described below:

| AREA | area factor (optional) (If not specified, the default value is 1.0.) |

| OFF | initial condition for the DC analysis (optional) |

| IC | initial condition (optional) (Used when a transient analysis is desired, which starts from other than the quiescent operating point.) |

| T | operating temperature of the device (optional) |

The process models can be either junction diodes or Schottky barrier diodes. Area factor scales the model parameters IS, RS, CJO, and IBV. VD is the initial voltage, and TEMP is the overriding temperature. Descriptions of the process model parameters are given in the following table:

| NAME | PARAMETER | UNITS | DEFAULT | NOTES |

|---|---|---|---|---|

| IS | saturation current | A | 1e-14 | |

| TNOM | parameter measurement temperature | deg C | 27 | |

| RS | ohmic resistance | Ohms | 0 | |

| N | emission coefficient | - | 1 | |

| TT | transit-time | sec | 0 | |

| CJO | zero-bias junction capacitance | F | 0 | |

| VJ | junction potential | V | 1 | |

| M | grading coefficient | - | 0.5 | |

| EG | activation energy | eV | 1.11 | |

| XTI | saturation current temp. exp. | - | 3.0 | |

| KF | flicker noise coefficient | - | 0 | |

| AF | flicker noise exponent | - | 1 | |

| FC | forward bias junction fit parameter | - | 0.5 | |

| BV | reverse breakdown voltage | V | inf | |

| IBV | current at breakdown voltage | A | 1e-3 |

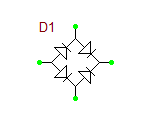

Diode Bridge

This four-pin device is a bridge configuration of four generic diodes.

Parameters:

| NAME | PARAMETER | UNITS | DEFAULT | NOTES |

|---|---|---|---|---|

| IS | saturation current | A | 1e-14 | |

| RS | ohmic resistance | Ohms | 0 | |

| N | emission coefficient | - | 1 | |

| TT | transit-time | sec | 0 | |

| CJO | zero-bias junction capacitance | F | 10p | |

| VJ | junction potential | V | 1 | |

| M | grading coefficient | - | 0.5 | |

| BV | reverse breakdown voltage | V | 1000 | |

| IBV | current at breakdown voltage | A | 1e-3 | |

| TNOM | parameter measurement temperature | deg C | 27 |

Doubly Center-Tapped Ferrite Core Transformer

This six-pin four-port device models a doubly center-tapped physical transformer with a magnetic ferrite core. Its model is based on XSPICE's magnetic core and inductive coupling models. For this device you need to specify physical parameters like cross sectional area, core length and number of primary and secondary turns. The physical model of the magnetic device is defined by two vectors: magnetic field intensity H in A/m and magnetic flux density B (also known as magnetic induction) in Tesla. The default array values are:

H_array = [-250 -100 -50 -37.5 -25 -12.5 0 12.5 25 37.5 50 100 250]

B_array = [-0.375 -0.36 -0.32 -0.29 -0.24 -0.15 0 0.15 0.24 0.29 0.32 0.36 0.375]

To change the value of H/B arrays, open the subcircuit model dialog by clicking the View Subcircuit button and edit its text.

Parameters:

| NAME | PARAMETER | UNITS | DEFAULT | NOTES |

|---|---|---|---|---|

| n_prim | number of full-winding primary inductor coupling turns | - | 100 | required |

| n_sec | number of full-winding secondary inductor coupling turns | - | 100 | required |

| area | cross-sectional area | m2 | 1e-5 | |

| length | core length | m | 0.01 |

DPDT Switch

This is an 8-pin device that models a double-pole double-throw switch. It has two input signals and four output pins. When the control voltage is at the high state, the first and second input voltages are transferred to the first and third output pins, respectively. When the control voltage is at the low state, the first and second input voltages are transferred to the second and fourth output pins, respectively.

Parameters:

| NAME | PARAMETER | UNITS | DEFAULT | NOTES |

|---|---|---|---|---|

| von | turn-on voltage | V | 3.3 | |

| voff | turn-off voltage | V | 0.3 | |

| vt | threshold voltage | V | 1.0 | |

| ron | on resistance | Ohms | 1.0 | |

| roff | off resistance | Ohms | 1Gig |

DPST Switch

This is a 6-pin device that models a double-pole single-throw switch. It has two input signals and two output signals. When the switch on, the first and second input voltages are transferred to the first and second output pins, respectively. When the switch is off, the output pin do not receive any input signals.

Parameters:

| NAME | PARAMETER | UNITS | DEFAULT | NOTES |

|---|---|---|---|---|

| von | turn-on voltage | V | 3.3 | |

| voff | turn-off voltage | V | 0.3 | |

| vt | threshold voltage | V | 1.0 | |

| ron | on resistance | Ohms | 1.0 | |

| roff | off resistance | Ohms | 1Gig |

Ferrite Core Transformer

This four-pin two-port device models a physical transformer with a magnetic ferrite core. Its model is based on XSPICE's magnetic core and inductive coupling models. For this device you need to specify physical parameters like cross sectional area, core length and number of primary and secondary turns. The physical model of the magnetic device is defined by two vectors: magnetic field intensity H in A/m and magnetic flux density B (also known as magnetic induction) in Tesla. The default array values are:

H_array = [-250 -100 -50 -37.5 -25 -12.5 0 12.5 25 37.5 50 100 250]

B_array = [-0.375 -0.36 -0.32 -0.29 -0.24 -0.15 0 0.15 0.24 0.29 0.32 0.36 0.375]

To change the value of H/B arrays, open the subcircuit model dialog by clicking the View Subcircuit button and edit its text.

Parameters:

| NAME | PARAMETER | UNITS | DEFAULT | NOTES |

|---|---|---|---|---|

| n_prim | number of primary turns | - | 100 | required |

| n_sec | number of secondary turns | - | 100 | required |

| area | cross-sectional area | m2 | 1e-5 | |

| length | core length | m | 0.01 |

FM Modulated Source

This is a voltage source with a single-tone frequency modulated waveform. The FM modulation index MDI is defined as the ratio of maximum frequency deviation to maximum signal amplitude.

Parameters:

| NAME | PARAMETER | UNIT | DEFAULT | NOTES |

|---|---|---|---|---|

| V0 | offset | V | 0 | |

| VA | amplitude | V | 1 | |

| FC | carrier frequency | Hz | 1 | required |

| MDI | modulation index | - | 0 | required |

| FS | signal frequency | Hz | 1 | required |

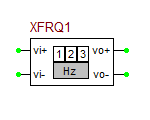

Frequency Meter

The Frequency Meter is a four-pin shunt device that is connected in parallel with an AC source just like a voltmeter and measures the operating frequency of the AC circuit. The input pins are connected across the AC source. The voltage across the output pins is equal to the frequency of the source in Hertz within a scale factor SF. Note that the Frequency Meter is designed to work with a single-tone AC source of unit amplitude. If the amplitude of the source is not one, multiply the SF parameter by the non-unit source amplitude value. The output voltage of the Frequency Meter can be used in conjunction with linear or nonlinear dependent sources to model frequency-dependent quantities.

Model Identifier: fmeter

Parameters:

The only parameter is the scale factor SF with a default value of 1.0. Set SF = 1e-6 to read out the frequency in MHz. Set SF = 1e-9 to read out the frequency in GHz. Set SF = 6.283185 (2*pi) to read out the angular frequency ω in radian/s.

Fuse

This is a 2-pin interactive current-controlled switch. If the current passing through the fuse is less than a specified threshold current, the switch is closed. If the current exceeds the threshold level, the fuse breaks and remains open thereafter. The device's symbol changes to display its state.

Parameters:

| NAME | PARAMETER | UNITS | DEFAULT | NOTES |

|---|---|---|---|---|

| r | resistance when intact | Ohms | 1.0 | |

| i_thresh | threshold current | A | 1.0 |

Ground

Ground has a voltage of zero (0) and is used as a reference to compute electrical values in the circuit. All circuits must be grounded to be properly simulated. There is no limit on the number of grounds you may use in a circuit. All components connected to ground are referenced to a common point and treated as linked through ground.

Hysteresis Block (XSPICE)

The Hysteresis block is a simple buffer stage that provides hysteresis of the output with respect to the input. The in_low and in_high parameter values. The output values are limited to out_lower_limit and out_upper_limit. The value of \93hyst\94 is added to the in_low and in_high points in order to specify the points at which the slope of the hysteresis function would normally change abruptly as the input transitions from a low to a high value. Likewise, the value of \93hyst\94 is subtracted from the in_high and in_low values in order to specify the points at which the slope of the hysteresis function would normally change abruptly as the input transitions from a high to a low value. In fact, the slope of the hysteresis function is never allowed to change abruptly but is smoothly varied whenever the input_dowmain smoothing parameter is set greater than zero.

Model Identifier: hyst

Netlist Format:

A<device_name> <in_pin> <out_pin> <model_name>

.model <model_name> hyst {<param1 = value> < param2 = value> ...}

Example:

A1 1 2 hysteresis_block

.model hysteresis_block hyst in_low = 0.0 in_high = 1.0

Parameters:

| Name | Description | Default |

|---|---|---|

| In_low | input low value | 0.0 |

| in_high | input high value | 1.0 |

| hyst | hysteresis | 0.1 |

| out_lower_limit | output lower limit | 0.0 |

| out_upper_limit | output upper limit | 1.0 |

| input_domain | input smoothing domain | 0.01 |

| fraction | smoothing fraction/absolute value switch | true |

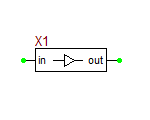

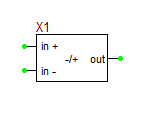

Ideal Buffer Block

This model is an ideal buffer block with a default unity gain.

Parameters:

| NAME | PARAMETER | UNITS | DEFAULT | NOTES |

|---|---|---|---|---|

| r_in | input resistance | Ω | 1G | |

| r_out | output resistance | Ω | 1u | |

| gain | gain | - | 1.0 |

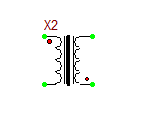

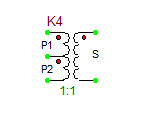

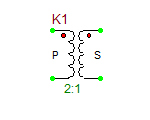

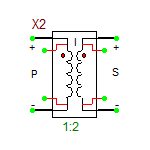

Ideal Center-Tapped Transformer with Push-Pull Input

The ideal center-tapped transformer with push-pull input is a five-pin three-port device with two primary input ports and one secondary output port. Its model is based on the Ideal Transformer, and the relationship between its primary and secondary voltages is given by:

[math] \frac{v_P1}{v_S} = \frac{v_P2}{v_S} = n [/math]

where vS is the secondary voltage, vP1 is measured between the top primary pin P1 and the center tap pin, and vP2 is measured between the center tap pin and the bottom primary pin P2. The red dots show the polarity of the windings on each side. This model has one parameter: ratio = n = NP1/NS = NP2/NS, which represents the primary-to-secondary (half-winding) turns ratio.

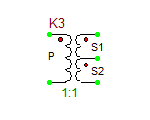

Ideal Center-Tapped Transformer with Push-Pull Output

The ideal center-tapped transformer with push-pull output is a five-pin three-port device with one primary input port and two secondary output ports. Its model is based on the Ideal Transformer, and the relationship between its primary and secondary voltages is given by:

[math] \frac{v_P}{v_{S1}} = \frac{v_P}{v_{S2}} = n [/math]

where vP is the primary voltage, vS1 is measured between the top secondary pin S1 and the center tap pin, and vS2 is measured between the center tap pin and the bottom secondary pin S2. The red dots show the polarity of the windings on each side. This model has one parameter: ratio = n = NP/NS1 = NP/NS2, which represents the primary-to-secondary (half-winding) turns ratio.

Ideal Comparator Block

This block is an ideal two-signal voltage comparator with a default unity gain. It has a binary output that takes a value of 0V if vpos < vneg and takes a value of 1V if vpos > vneg. If vpos = vneg, the output voltage is 0.5V.

Parameters:

| NAME | PARAMETER | UNITS | DEFAULT | NOTES |

|---|---|---|---|---|

| gain | comparator gain | - | 1.0 |

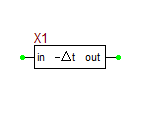

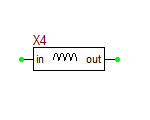

Ideal Delay Block

This model is an ideal signal delay block based on an ideal delay line model.

Parameters:

| NAME | PARAMETER | UNITS | DEFAULT | NOTES |

|---|---|---|---|---|

| delay | time delay | sec | 1u |

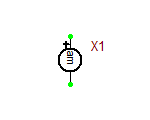

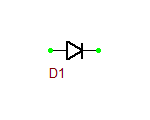

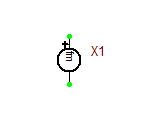

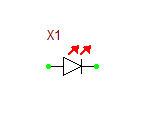

Ideal Diode

This 2-pin device is a very basic and primitive model of a diode as a rectifier or switch. When the voltage across the device's terminals is positive, it acts as a short circuit. When the voltage across the device's terminals is negative, it acts as an open circuit.

Parameters:

None

Ideal Full-Wave Rectifier Block

This block rectifies an input signal at both positive and negative cycles with a default unity gain.

Parameters:

| NAME | PARAMETER | UNITS | DEFAULT | NOTES |

|---|---|---|---|---|

| gain | rectifier gain | - | 1.0 |

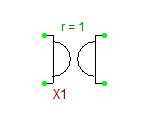

Ideal Gyrator Block

An ideal gyrator is a linear two-port device which couples the current on one port to the voltage on the other and vice versa. The instantaneous voltages and currents instantaneous are related by:

- [math]v_{out}(t) = R \cdot i_{in}(t) [/math]

- [math]v_{in}(t) = - R \cdot i_{out}(t) [/math]

The ideal gyrator acts as an impedance inverter.

Parameters:

| NAME | PARAMETER | UNITS | DEFAULT | NOTES |

|---|---|---|---|---|

| r | gyration resistance | Ω | 1.0 |

Ideal Half-Wave Rectifier Block

This block rectifies an input signal at positive cycles with a default unity gain. Its output at negative cycles is zero.

Parameters:

| NAME | PARAMETER | UNITS | DEFAULT | NOTES |

|---|---|---|---|---|

| gain | rectifier gain | - | 1.0 |

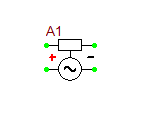

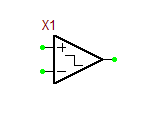

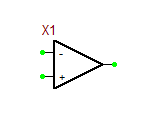

Ideal Operational Amplifier (Op-Amp)

This is a very basic and primitive model of an operational amplifier. It has only one parameter, open loop gain with a default value of 50,000, which is adequate for most cases. The ideal Op-Amp device doesn't require any DC bias voltages.

Parameters:

| NAME | PARAMETER | UNIT | DEFAULT | NOTES |

|---|---|---|---|---|

| A | open loop gain | - | 50,000 |

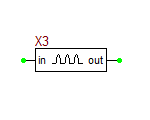

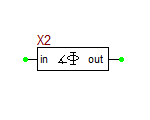

Ideal Phase Shifter Block

This model is an ideal signal phase shifter block based on an ideal transmission line segment model. It is frequency-dependent and the signal phase shift is accurate only around the specified center frequency.

Parameters:

| NAME | PARAMETER | UNITS | DEFAULT | NOTES |

|---|---|---|---|---|

| phi | phase shift | deg | 90 | must be positive |

| fo | center frequency | Hz | 1Meg |

Ideal Polarity Detector Block

This 3-pin device measures the difference signal Δv = vpos - vneg and produces a binary output ±A according to the sign of Δv, where A is a user defined amplitude.

Parameters:

| NAME | PARAMETER | UNITS | DEFAULT | NOTES |

|---|---|---|---|---|

| MaxVal | output amplitude | V | 1 |

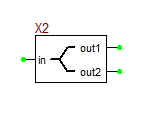

Ideal Splitter Block

This model is an ideal signal splitter block with a default one-half split ratio. It splits the input signal by a ratio of k:(1-k).

Parameters:

| NAME | PARAMETER | UNITS | DEFAULT | NOTES |

|---|---|---|---|---|

| k | split ratio | - | 0.5 |

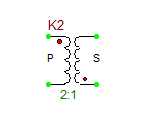

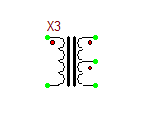

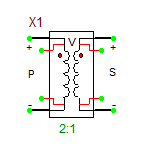

Ideal Transformer

The ideal transformer is a four-pin two-port device with the following relationship between the voltages and currents at its primary and secondary ports:

[math] \frac{v_P}{v_S} = - \frac{i_S}{i_P} = \frac{N_P}{N_S} = n [/math]

where vP, iP, NP are the primary voltage, current and number of turns, respectively, and vS, iS, NS are the secondary voltage, current and number of turns, respectively. The red dots show the polarity of the windings on each side. This model has one parameter: ratio = n = NP/NS, which represents the primary-to-secondary turns ratio. Note that the ideal transformer model is defined based on controlled sources and does not involve any magnetic physical parameters as opposed to mutual inductors or ferrite core transformer.

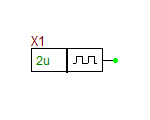

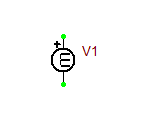

Impulse Generator

This is a voltage source that generates a periodic impulse train with oscillating between zero and a user defined maximum voltage level.

Parameters:

| NAME | PARAMETER | UNIT | DEFAULT | NOTES |

|---|---|---|---|---|

| T | impulse period | sec | 1u | required |

| duty_cycle | impulse duty cycle | - | 0.01 | required |

| max_val | maximum output voltage level | V | 1 | |

| delay | delay time | sec | 0 |

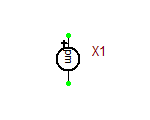

Inductance Meter

The Inductance Meter measures the total inductance between a circuit node and the ground. The input pin of the device is connected to the measurement node. The output voltage of the device is then a scaled value equal to the total inductance seen on its input multiplied by the gain parameter. This model is primarily intended as a building block for other models which must sense an inductance value and alter their behavior based upon it. Care must be exercised when connecting an Inductance Meter to the inductors of a circuit. This is due to the fact that inductors are treated by SPICE as current sources. This can cause a problem when an inductor is connected in series with a current source, or in series with a voltmeter, or in series with another inductor.

Model Identifier: lmeter

Netlist Format:

A<device_name> <in_pin> <out_pin> <model_name>

.model <model_name> imeter {<gain = value>}

Example:

A1 1 2 inductance_meter

.model inductance_meter lmeter gain = 1

Parameters:

The only parameter is the gain with a default value of 1.0.

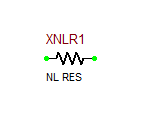

Inductive Coupler Block

The Inductive Coupler Block couples any two existing inductors. This block doesn't have any pins because it doesn't actually represent inductors, only the coupling between them. This is useful if you want to couple two inductors that are in different parts of the circuit, or if you want to couple more than two inductors together. In the latter case, use more than one of these, with each one coupling a pair of inductors.

The standard parameters are Inductor1, Inductor2, and k. Inductor1 is the name of first inductor, Inductor2 is the name of the second inductor, and k is the coefficient of coupling, 0 < k ≤ 1.

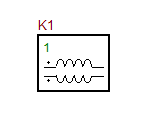

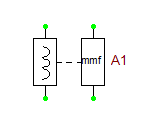

Inductive Coupling (XSPICE)

This function is a conceptual model which is used as a building block to create a wide variety of inductive and magnetic circuit models. This function is normally used in conjunction with the “core” model, but it can also be used with resistors, hysteresis blocks, etc. to build up systems which mock the behavior of linear and nonlinear components. The lcouple takes as an input (on the “l” port) a current. This current value is multiplied by the num_turns value, N, to produce an output value (a voltage value which appears on the mmf_out port). The mmf_out acts similar to a magnetomotive force in a magnetic circuit; when the lcouple is connected to the “core” model, or to some other resistive device, a current will flow. This current value (which is modulated by whatever the lcouple is connected to) is then used by the lcouple to calculate a voltage “seen” at the “l” port. The voltage is a function of the derivative with respect to time of the current value seen at mmf_out.

The most common use for lcouple will be as a building block in the construction of transformer models. To create a transformer with a single input and a single output, you would require two lcouple models plus one “core” model.

Example:

A1 (1 0) (2 3) lcouple1

.model lcouple1 lcouple ( num_turns = 10 )

Parameters:

| NAME | PARAMETER | UNITS | DEFAULT | NOTES |

|---|---|---|---|---|

| num_turns | number of turns | - | 1 | required |

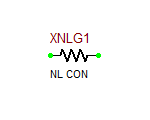

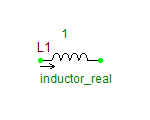

Inductor

Inductors are used to store magnetic energy. An inductor's ability to counteract current changes passing through it is called its inductance (L), which is measured in Henrys. In a (steady-state) DC analysis, the inductor acts like a short circuit. It is indeed treated as a current source, which can be problematic if an inductor is connected in series with a current source, or in series with a voltmeter, or in series with another inductor. The resistor may be of negligible value or one that accounts for the coil resistance of the inductor. In AC and transient analyses, the inductor develops a voltage across it in response to the changing magnetic flux within its coil.

An inductor's transient behavior is described by the equation:

v(t) = L*(di(t)/dt)

The inductor's initial condition is optional. It is the initial value of the inductor current in Amperes that flows from node N+ through the inductor to node N-. The only time that the initial current matters is when the simulator performs a transient analysis, and the "Use Initial Conditions" checkbox is checked.

An inductor's AC behavior is described by the equation:

v = j ω * L * i

All inductor names must begin with L.

Netlist Format:

L<device_name> <N+> <N-> <value>

Example:

L1 1 2 10u

Inductor with Ferrite Core

This 2-pin device models a physical inductor with a magnetic ferrite core. Its model is based on XSPICE's magnetic core and inductive coupling models. Unlike the standard inductor device, you do not specify an inductance value for the inductor with ferrite core. Rather, you specify physical parameters like cross sectional area, core length and number of turns. The physical model of the magnetic device is defined by two vectors: magnetic field intensity H in A/m and magnetic flux density B (also known as magnetic induction) in Tesla. The default array values are:

H_array = [-250 -100 -50 -37.5 -25 -12.5 0 12.5 25 37.5 50 100 250]

B_array = [-0.375 -0.36 -0.32 -0.29 -0.24 -0.15 0 0.15 0.24 0.29 0.32 0.36 0.375]

To change the value of H/B arrays, open the subcircuit model dialog by clicking the View Subcircuit button and edit its text.

Parameters:

| NAME | PARAMETER | UNITS | DEFAULT | NOTES |

|---|---|---|---|---|

| n_turns | number of turns | - | 100 | required |

| area | cross-sectional area | m2 | 1e-5 | |

| length | core length | m | 0.01 |

Insulated Gate Bipolar Transistor (IGBT)

This is a 3-pin parameterized Insulated Gate Bipolar Transistor (IGBT) device with three pins: Collector(C), Gate (G), and Emitter (E). It is primarily used as a fast electronic switch. The IGBT combines the simple gate-drive characteristics of MOSFETs with the high-current and low-saturation-voltage capability of bipolar transistors. The device's model consists of an isolated gate FET for the control input, and a PNP bipolar power transistor as a switch. To further modify the internal device models, open the subcircuit model dialog by clicking the View Subcircuit button and edit its text.

Parameters:

| NAME | PARAMETER | UNITS | DEFAULT | NOTES |

|---|---|---|---|---|

| cap | parasitic capacitance | F | 1n | |

| rg | gate resistance | Ohms | 5 | |

| re | emitter resistance | Ohms | 0.05 | |

| bf | pnp transistor forward beta | - | 1 | |

| vto | MOSFET threshold voltage | V | 5 | |

| kt | MOSFET transconductance | - | 2.99 | |

| cgso | MOSFET voltage gate-source overlap capacitance | F | 5u | |

| nd | diode emission coefficient | - | 50 | |

| cjo | diode junction capacitance | F | 1n |

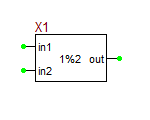

Integer Modulo Block

This 3-pin device requires a voltage with an integer value on its second input pin. It produces a voltage equal to vin1 % vin2 and sends it to the output with a default unity gain.

Parameters:

| NAME | PARAMETER | UNITS | DEFAULT | NOTES |

|---|---|---|---|---|

| gain | gain | - | 1.0 |

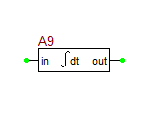

Integrator Block

The Integrator Gain and input offset parameters are also included to allow for tailoring of the required signa. Output upper and lower limits are also included to prevent convergence errors resulting from excessively large output values. Note that these limits specify integrator behavior similar to that found in an operational amplifier-based integration stage, in that once a limit is reached, additional storage does not occur. Thus the input of a negative value to an integrator which is currently driving at the out_upper_limit level will immediately cause a drop in the output, regardless of how long the integrator was previously summing positive inputs. The incremental value of output below the output_upper_limit and above the output_lower_limit at which smoothing begins is specified via the limit_range parameter. In AC analysis, the value returned is equal to the gain divided by the radian frequency of analysis.

Note that truncation error checking is included in the \93int\94 block. This should provide for a more accurate simulation for the time integration function, since the model will inherently request smaller time increments between simulation points if truncation errors would otherwise be excessive.

Model Identifier: int

Netlist Format:

A<device_name> <in_pin> <out_pin> <model_name>

.model <model_name> int out_lower_limit = <value> out_upper_limit = <value> {<param1 = value> < param2 = value> ...}

Example:

A1 1 2 integrator_block

.model integrator_block int out_lower_limit = -1t out_upper_limit = 1t

Parameters:

| NAME | PARAMETER | UNITS | DEFAULT | NOTES |

|---|---|---|---|---|

| gain | gain | - | 1.0 | |

| in_offset | output offset | V | 0.0 | |

| out_lower_limit | output lower limit | V | -1t | required |

| out_upper_limit | output upper limit | V | 1t | required |

| limit_range | upper and lower limit smoothing range | - | 1.0e-6 | |

| out_ic | output initial condition | V | 0.0 |

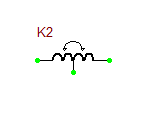

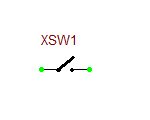

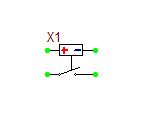

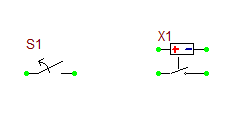

Interactive Switch

This device is an interactive switch that can be closed or opened either directly from the Schematic Editor by clicking on its symbol or from the Instrument Panel.

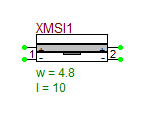

Interdigital Capacitor

This is a four-pin, two-port device that models a planar interdigital capacitor.

Model Identifier: interdigital

Parameters:

| NAME | PARAMETER | UNITS | DEFAULT | NOTES |

|---|---|---|---|---|

| w | finger strip width | mm | 0.1 | |

| s | finger strip spacing | mm | 0.1 | |

| N | number of fingers | - | 5 | |

| l | capacitor length | mm | 1.0 | |

| h | substrate thickness | mm | 1.6 | |

| er | substrate relative permittivity | - | 2.2 |

Inverted Microstrip Line